AMD Steamroller - kompendium wiedzy na temat architektury

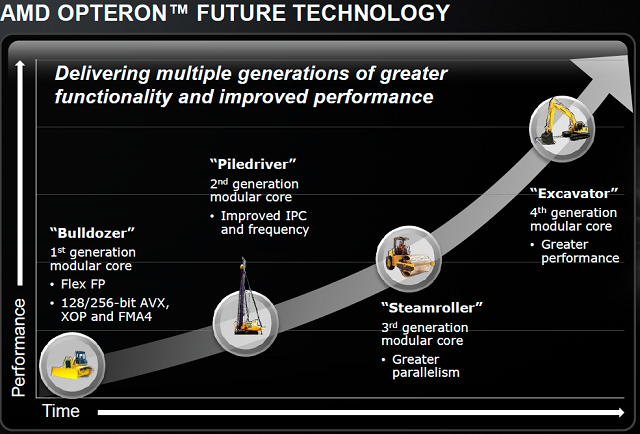

Wczoraj na konferencji Hot Chips, pan Mark Papermaster kierujący działem badawczym AMD, ujawnił oficjalne informacje na temat architektury procesorów x86 - Steamroller. Jest to trzecia generacja modularnych rdzeni. W tym roku czeka nas premiera procesorów opartych na jej drugiej odsłonie - Piledriver. Będą to układy APU Trinity oraz najnowsze procesory serii FX pozbawione modułu graficznego. Głównym zadaniem architektury Piledriver ma być zmniejszenie zużywanej energii elektrycznej przez procesor o 10-20% oraz pewna poprawa wydajności jednostki zajmującej się planowaniem zadań. Duże zmiany mają objąć jednostki odpowiedzialne za przewidywanie kolejnych instrukcji i ich wstępne ładowanie do pamięci podręcznej. W architekturze Steamroller z kolei skupiono się na poprawie wydajności jednego rdzenia i wdrożenie 28nm litografii.

Wczoraj na konferencji Hot Chips, pan Mark Papermaster kierujący działem badawczym AMD, ujawnił oficjalne informacje na temat architektury procesorów x86 - Steamroller. Jest to trzecia generacja modularnych rdzeni. W tym roku czeka nas premiera procesorów opartych na jej drugiej odsłonie - Piledriver. Będą to układy APU Trinity oraz najnowsze procesory serii FX pozbawione modułu graficznego. Głównym zadaniem architektury Piledriver ma być zmniejszenie zużywanej energii elektrycznej przez procesor o 10-20% oraz pewna poprawa wydajności jednostki zajmującej się planowaniem zadań. Duże zmiany mają objąć jednostki odpowiedzialne za przewidywanie kolejnych instrukcji i ich wstępne ładowanie do pamięci podręcznej. W architekturze Steamroller z kolei skupiono się na poprawie wydajności jednego rdzenia i wdrożenie 28nm litografii.

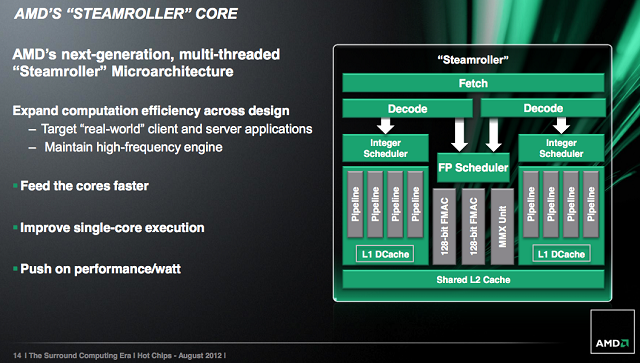

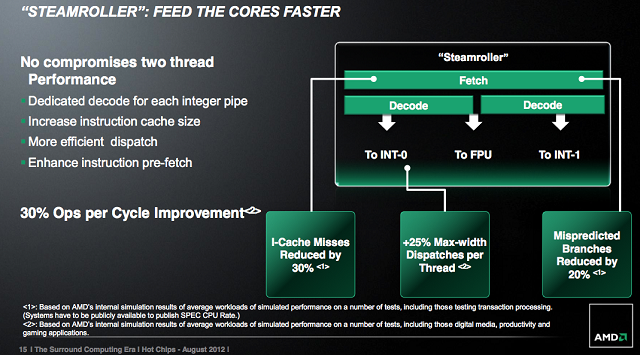

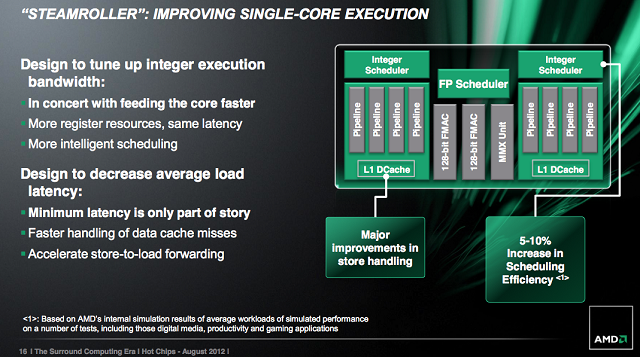

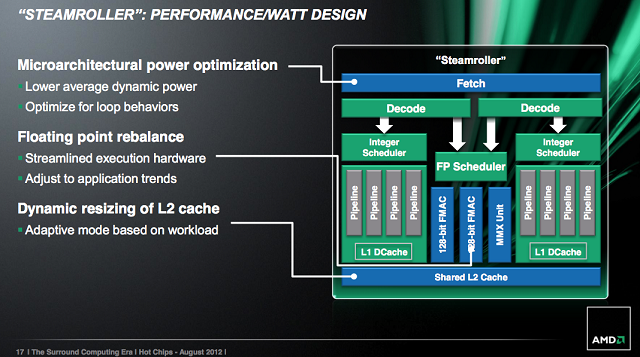

Jeden z największych problemów z jakimi borykał się Buldozer to współdzielone jednostki pobierania i dekodowania rozkazów dla obu rdzeni w module. Teraz każdy rdzeń będzie posiadał własny układ dekodujący rozkazy.

Niestety dalej jednostka FPU będzie współdzielona i nie zostaną wprowadzone żadne zmiany w sposobie wykonywania przez nią instrukcji. Tak samo będzie odnośnie dwóch jednostek integer znajdujących się w module.

Zmianie mają ulec rejestry dla obydwu jednostek, chociaż AMD nie podaje o ile zostały powiększone. Dwuargumentowe operacje ładowania zostały skompresowane tak, aby zajmować tylko jeden wpis w rejestrze. Powiększono też pamięć podręczną L1 przeznaczoną na instrukcje, ma to zmniejszyć o 30% błędne przewidywania instrukcji. Interfejs zarządzający pracą pamięci podręcznej pierwszego i drugiego poziomu również przeszedł pewne poprawki.

W architekturze Steamroller zostanie wprowadzona dynamiczna zmiana wartości pamięci podręcznej L2, w zależności od aktualnego obciążenia. Będzie ona podzielona na cztery części i nawet 3/4 pamięci L2 będzie mogło zostać wyłączone, jeśli zajdzie taka potrzeba. Ma to przynieść bardzo duże oszczędności energii w procesorach mobilnych. Niestety problem z wysokimi opóźnieniami pamięci podręcznej L2 i L3 nie został rozwiązany.

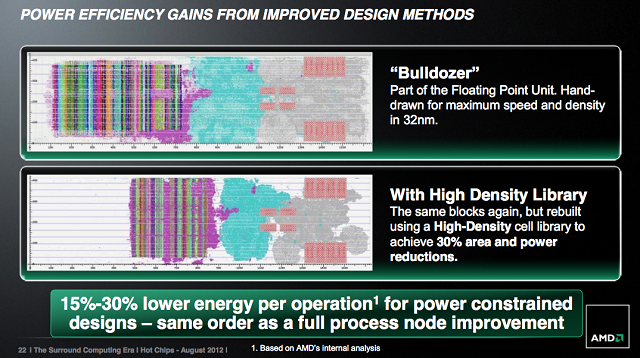

Przyszłe procesory AMD będą wykorzystywały wyższy poziom automatyzacji projektowania układów i gęstości upakowania tranzystorów, które są teraz wykorzystywane przy projektowaniu układów graficznych. W tym momencie AMD skorzystało z tej metody przy rdzeniach Bobcat. Pozwala to zaoszczędzić bardzo dużą powierzchnię krzemu kosztem niestety niższych zegarów procesora. Jako przykład AMD podało 30% zmniejszenie zajmowanej powierzchni i zużycia energii, gdy zastosowano te metody projektowania do 32nm jednostki FPU architektury Buldozer. Może to być atut nowych APU od AMD wykorzystywanych w mobilnych urządzeniach, gdzie wysoka częstotliwość pracy jest mniej ważna niż ogólne zużycie energii elektrycznej. Niestety ta technika projektowania nie zostanie zastosowana w Steamroller. Być może będzie wykorzystywał ją Excavator, planowany na 2014 rok.

Źródło: AnandTech

Powiązane publikacje

Informacje o procesorach Intel Arrow Lake - natywna obsługa Thunderbolt 4 dla chipsetu Z890 oraz powiększony cache L2

57

Intel Arrow Lake-S - w sprzedaży internetowej pojawiły się próbki inżynieryjne kolejnej generacji procesorów

24

HP Spectre x360 z Intel Lunar Lake pojawił się w bazie SiSoft Sandra - wydajność iGPU Battlemage stoi na wysokim poziomie

11

Intel twierdzi, że do niestabilności procesorów Core i9 w grach przyczynili się znacząco producenci płyt głównych

111